## TELECOMMUNICATION SPEECH A/D-CONVERTER COMPONENTS

### **Contents**

| l.   | Switching Components<br>µPD22100C                                                                                       | 4x4 Analog (Crosspoint Switch)                                          | 1 – 1                                     |

|------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------|

| II.  | Line Interface Components<br>μPD9513D/4D<br>μPD9516D/7D<br>Latch-up Considerations<br>μPD9601D/2D<br>Reliability Report | PCM COMBOs<br>PCM COMBOs<br>µPD951xD<br>PCM COMBOs<br>µPD951xD/µPD960xD | 2 - 1<br>3 - 1<br>4 - 1<br>5 - 1<br>6 - 1 |

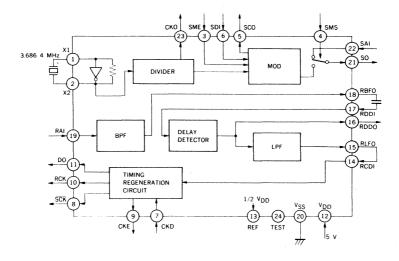

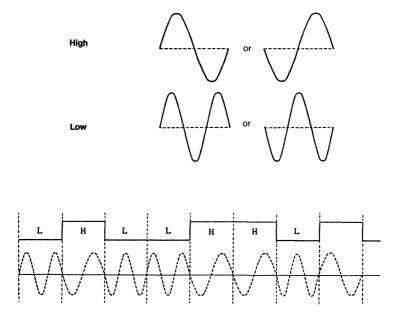

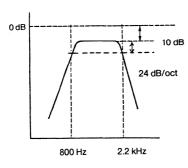

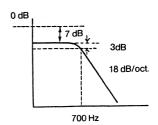

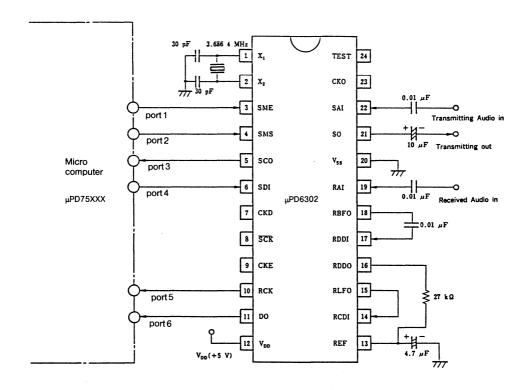

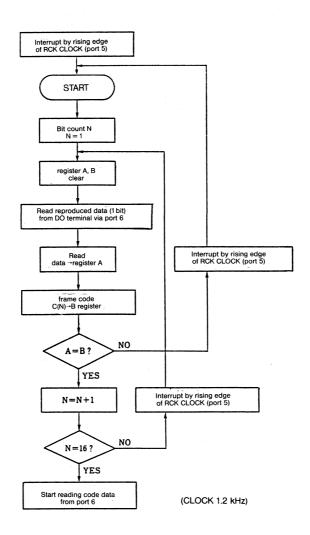

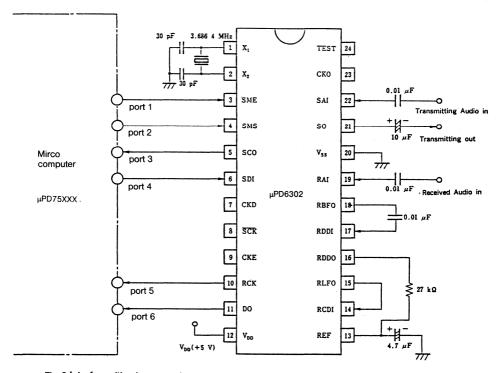

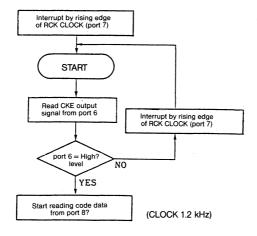

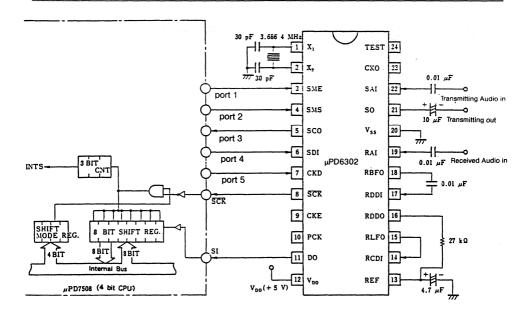

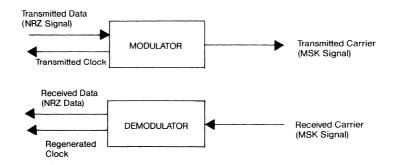

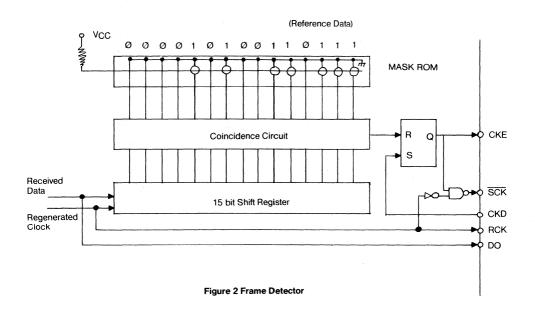

| III. | Transmission Components μPD6302G/CA                                                                                     | MSK (FFSK) MODEM                                                        | 7 – 1                                     |

| IV.  | Signal Processor Components<br>µPD7720A/77C20A/77P20                                                                    |                                                                         | 8 – 1                                     |

| V.   | Speech Synthese Components $\mu PD7755/56/59$                                                                           |                                                                         | 9 – 1                                     |

| VI   | . A/D And D/A Converter<br>μPC603 to μPD7004                                                                            |                                                                         | 10 – 1                                    |

## μPD22100C 4x4 CROSSPOINT SWITCH WITH CONTROL MEMORY

# 4 x 4 CROSSPOINT SWITCH WITH CONTROL MEMORY CMOS

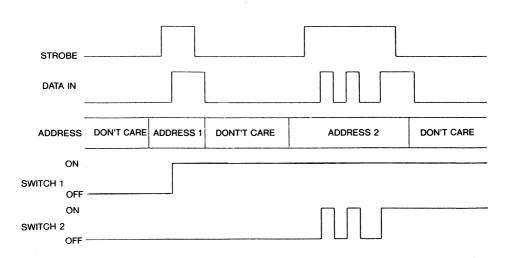

The  $\mu$ PD22100C consists of 16 crosspoint switches organized in 4 rows and 4 columns. Any of the 16 Switches can be selected by applying its address to the device and pulse to the strobe input. The selected crosspoint will turn on if during strobe, Data In was a one and will turn off if during strobe, Data In was a zero. Other switches are unaffected. On internal power-on reset turns off all-switches as power is applied.

Truth Table

| Г  |   | INPL  | ITS |   |   | SELECTED CHANNELS                                               |

|----|---|-------|-----|---|---|-----------------------------------------------------------------|

| s  |   |       |     |   | _ | YX0 YX1 YX2 YX3 YX0 YX1 YX2 YX3 YX0 YX1 YX2 YX3 YX0 YX1 YX2 YX3 |

|    |   |       |     |   |   |                                                                 |

| L  | X | X     | X   | X |   | NC ———                                                          |

| Н  | L | L     | L   | L | L | OFF NC                                                          |

| Н  | L | L     | L   | L |   |                                                                 |

| н  |   | _     |     |   |   | NC OFF NC                                                       |

| '' | - | _     |     |   |   |                                                                 |

| Н  | L | L     | L   | Н | Н | NC ON NC                                                        |

| Н  | L | L     | Н   | L | L | NCOFF NC                                                        |

| н  | L | L     | н   | L | н | NCON NC                                                         |

| н  | L | L     | н   | н | L | NC                                                              |

| н  | L | L     | н   | н | н | NCON NC                                                         |

|    |   |       |     |   |   |                                                                 |

| 1: | : | :     | Ċ   | : | : |                                                                 |

|    |   |       |     |   |   | •                                                               |

| 1: | : | :     |     |   | : | :                                                               |

|    |   |       |     |   |   |                                                                 |

|    |   | ٠     | •   | ٠ | • |                                                                 |

| :  |   | :     |     |   |   |                                                                 |

| Н  | H | H     | Н   | H | Ĺ | NC                                                              |

| I  |   | • • • |     | - | _ |                                                                 |

| Н  | Н | Н     | Н   | Н | Н | NC ———→ ON                                                      |

L : Low Level, H : High Level, NC : No Change, x : L or H

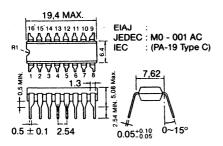

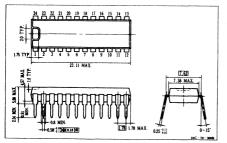

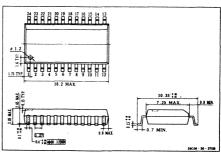

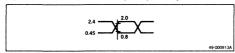

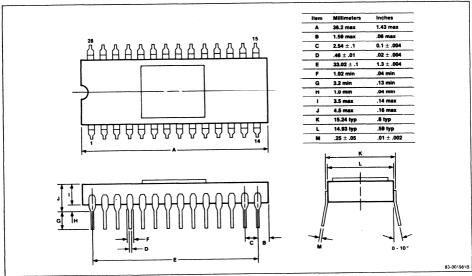

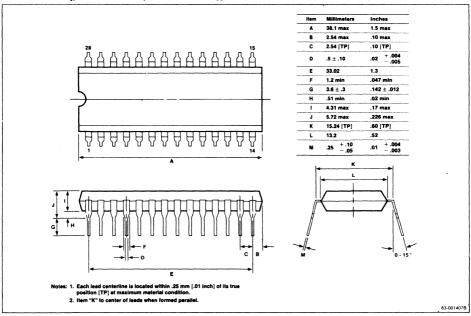

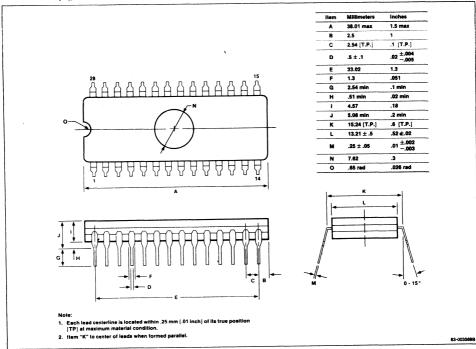

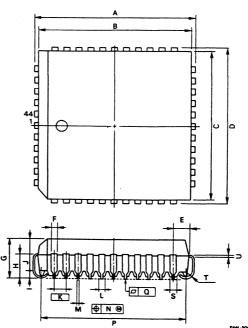

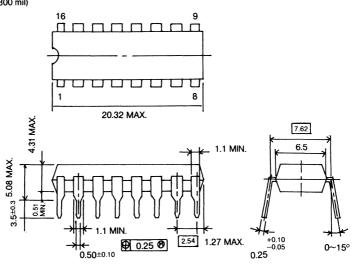

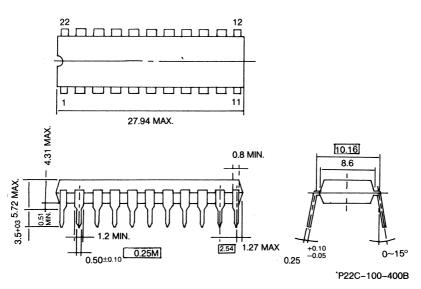

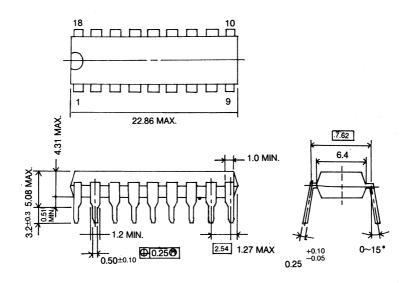

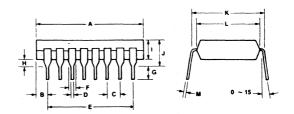

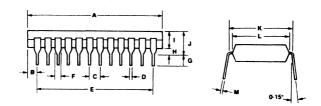

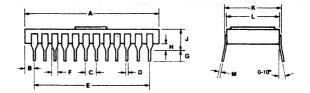

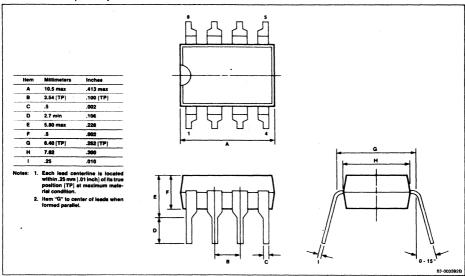

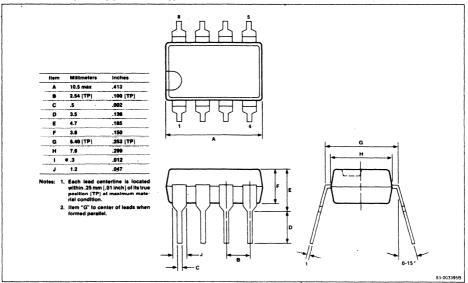

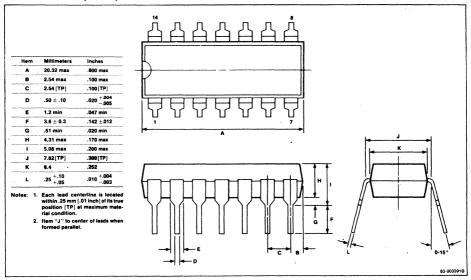

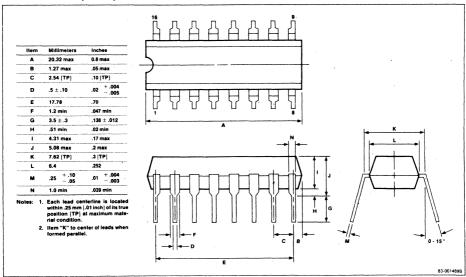

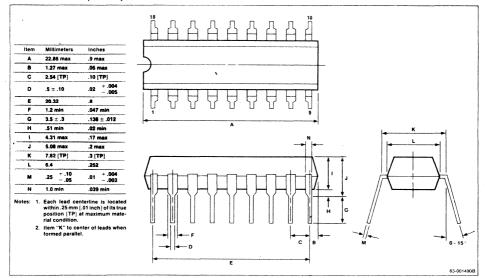

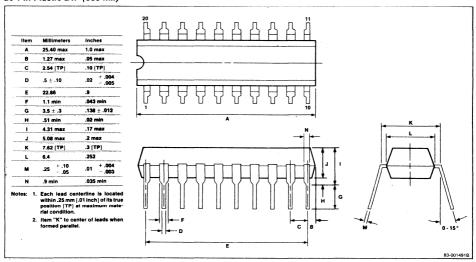

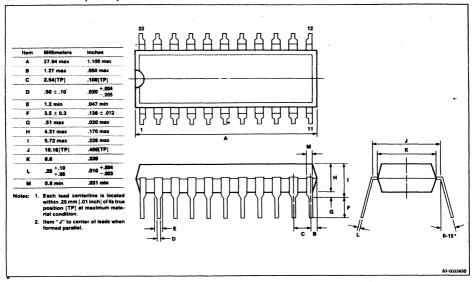

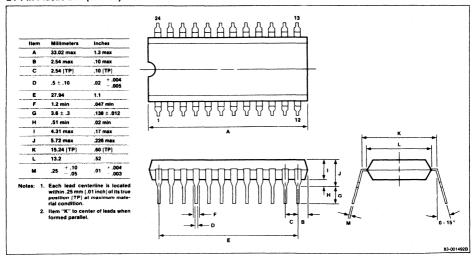

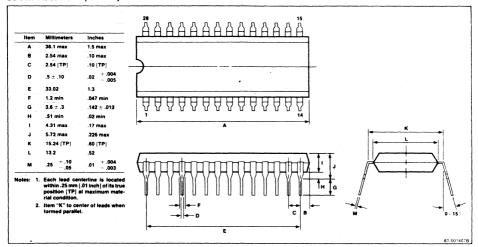

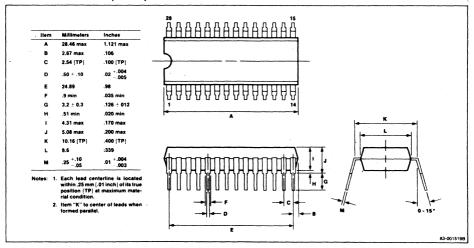

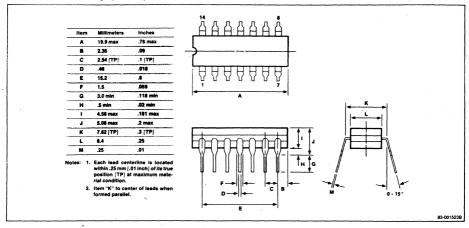

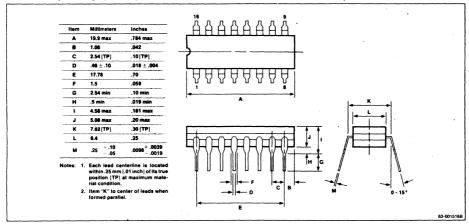

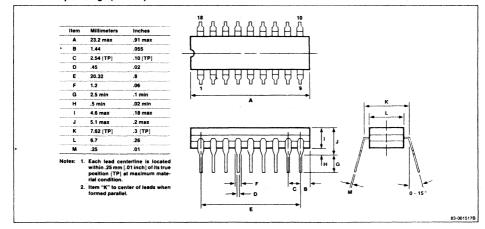

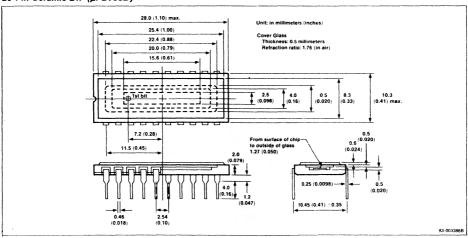

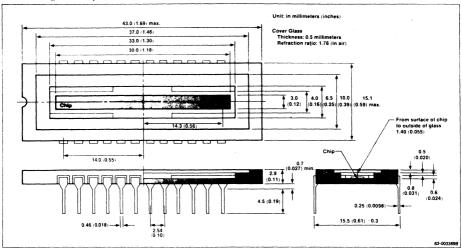

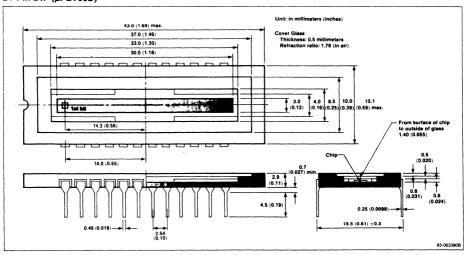

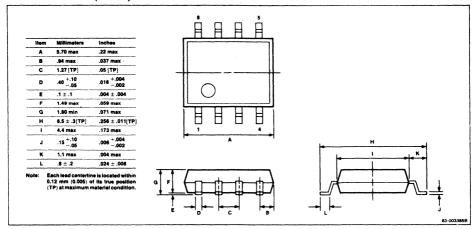

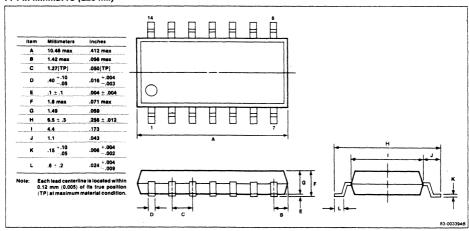

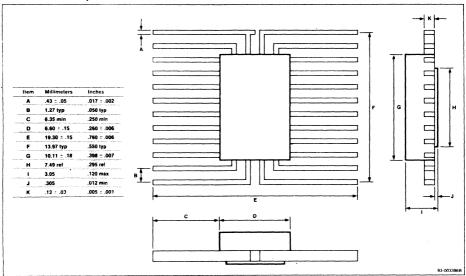

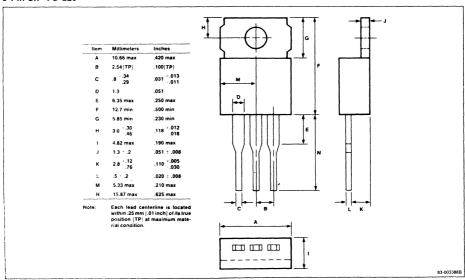

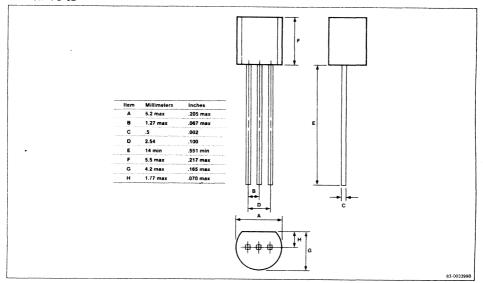

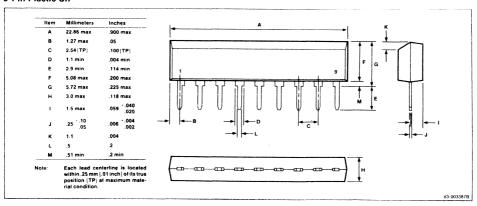

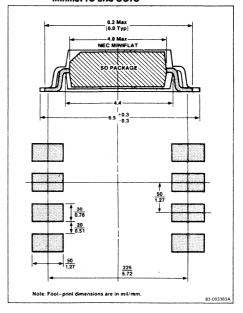

#### Package Dimensions (Unit: mm)

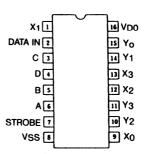

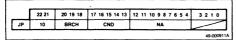

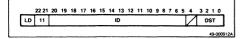

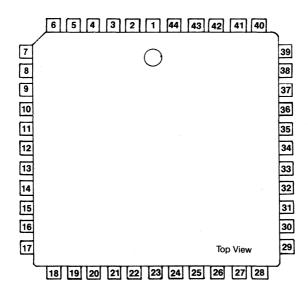

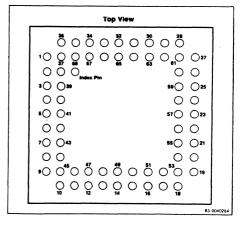

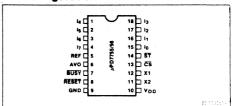

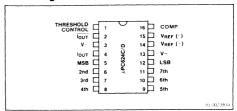

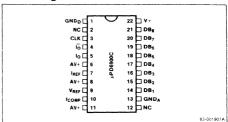

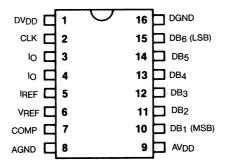

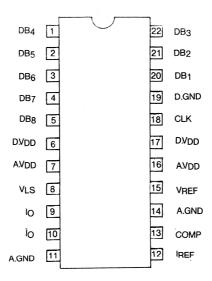

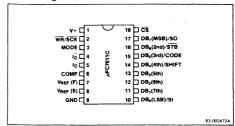

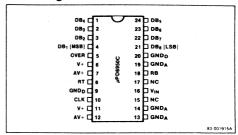

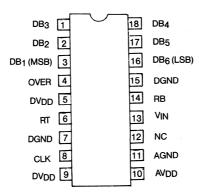

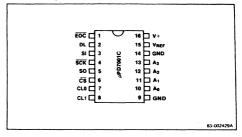

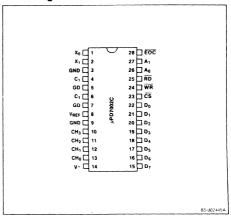

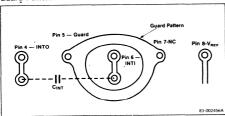

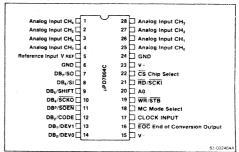

#### Connection Diagram (Top View)

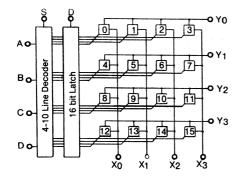

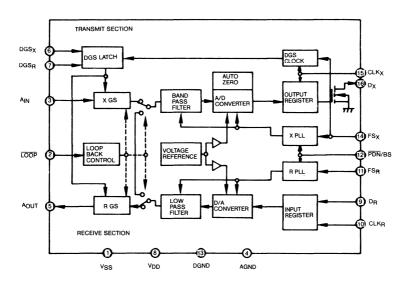

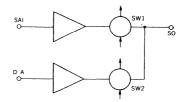

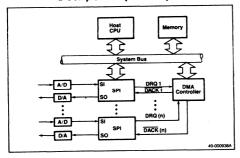

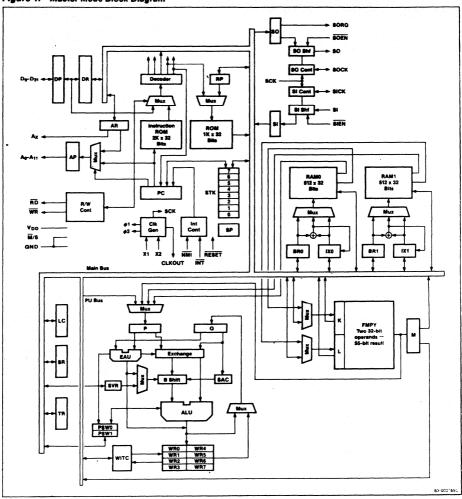

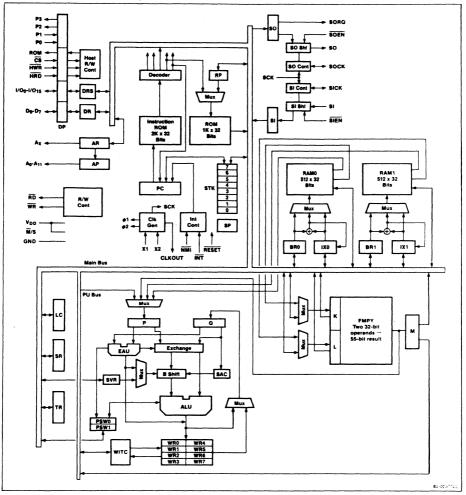

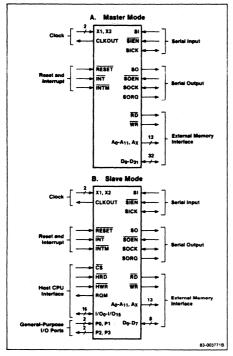

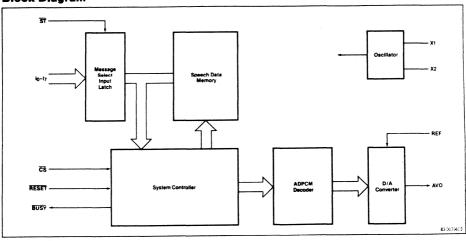

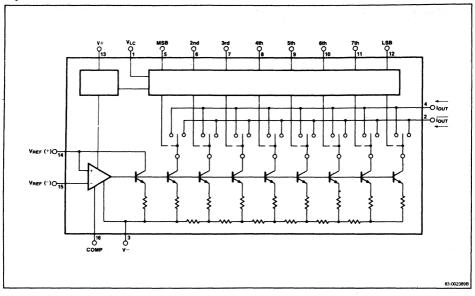

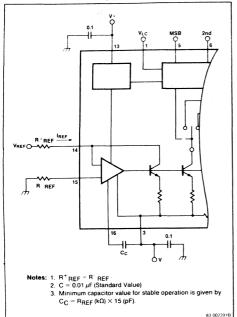

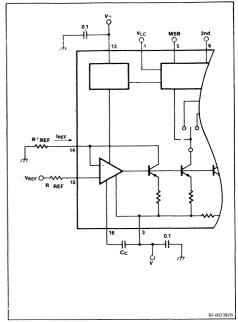

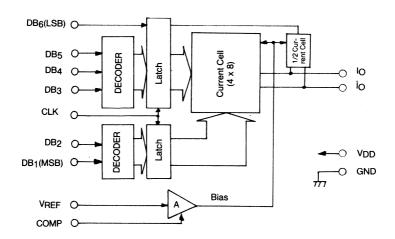

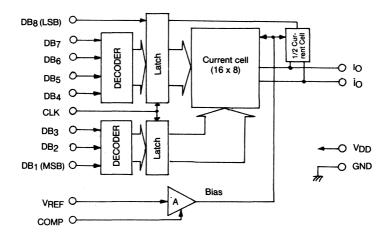

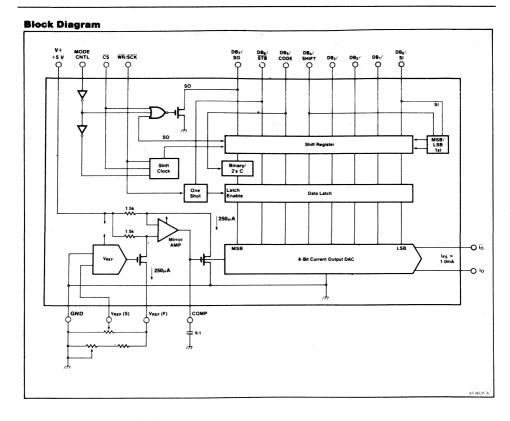

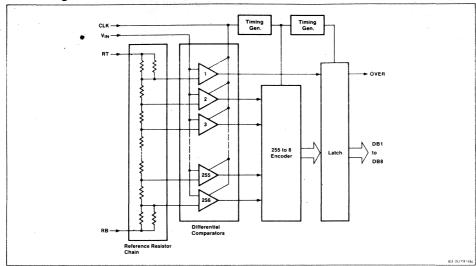

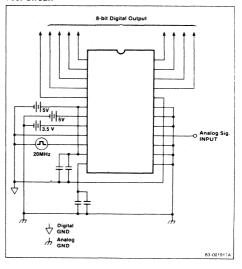

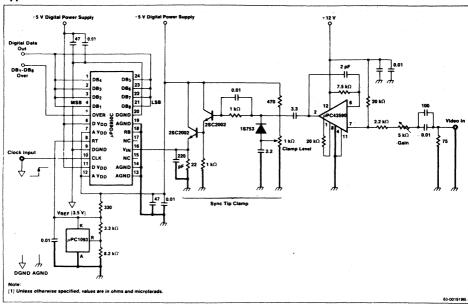

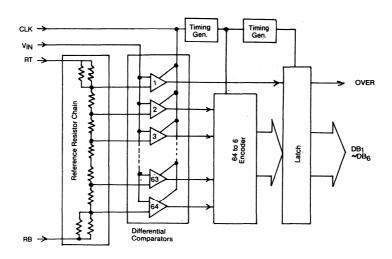

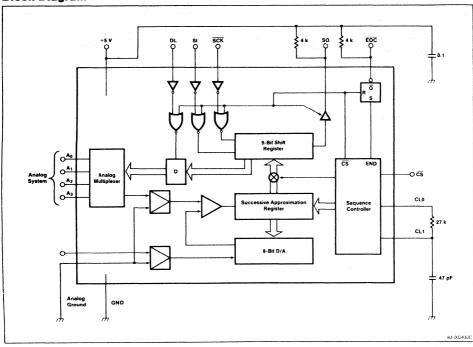

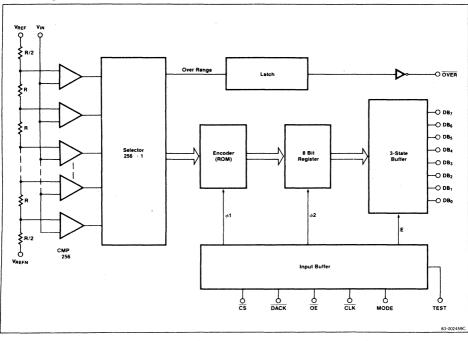

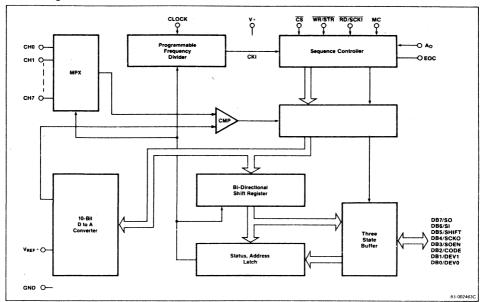

**Block Diagramm**

S : Strobe D : Data in

n : Analog Switch

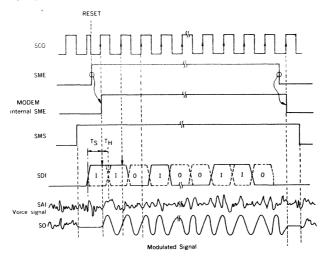

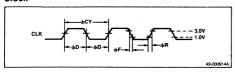

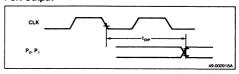

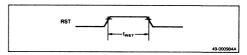

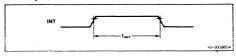

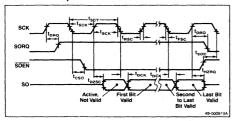

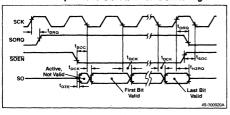

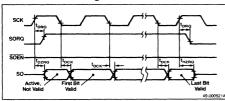

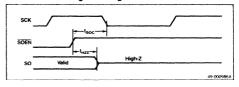

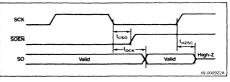

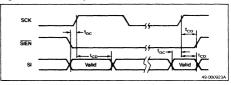

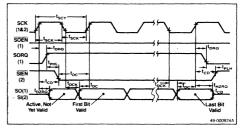

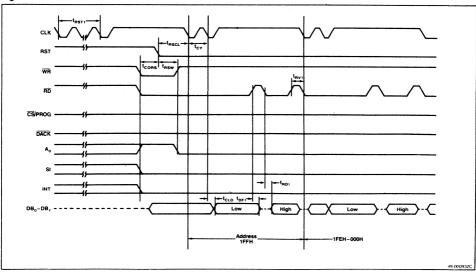

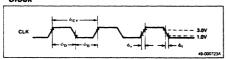

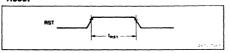

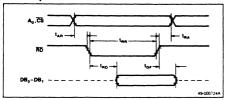

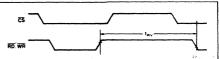

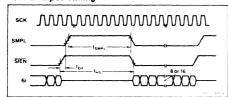

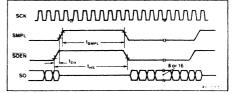

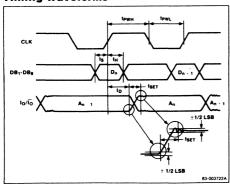

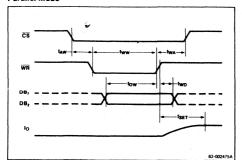

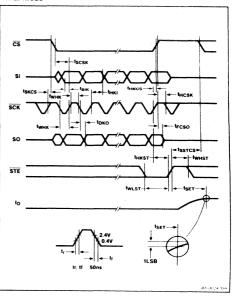

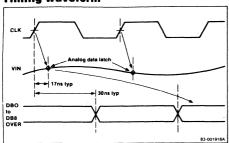

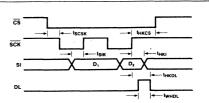

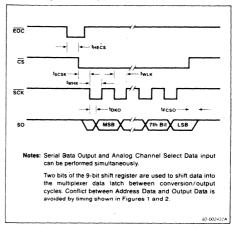

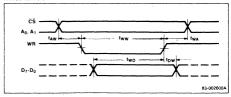

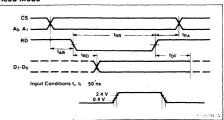

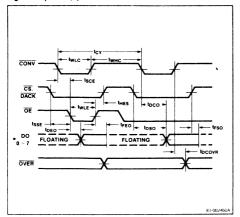

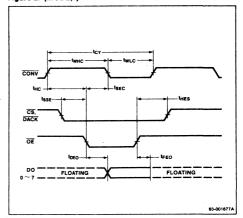

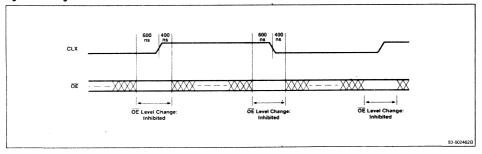

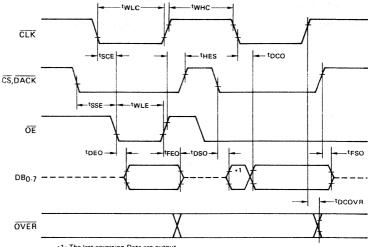

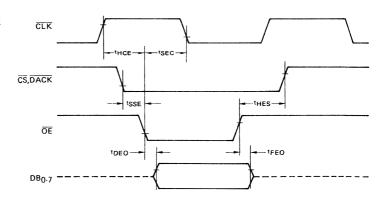

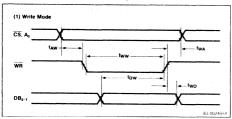

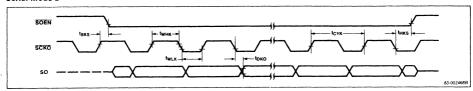

**Timing Chart**

### Absolute Maximum Ratings (Ta=25 °C)

| Item              | Symbol           | Absolute Maximum Ratings  | Unit |

|-------------------|------------------|---------------------------|------|

| DC Supply Voltage | VDD              | -0.5~+20                  | V    |

| Input Voltage     | VI               | -0.5∼V <sub>DD</sub> +0.5 | V    |

| Input Current     | II               | 10                        | mA   |

| Power Dissipation | PD               | 200                       | mW   |

| Operating Temp.   | Topt             | <b>-40∼+85</b>            | °C   |

| Storage Temp.     | T <sub>stg</sub> | - 65 ~ + 125              | °C   |

### Recommended Operating Conditions (Ta = -40/+ 85°C)

| Item              | Symbol | Conditions                                                         | Min.               | Тур. | Max.               | Unit |

|-------------------|--------|--------------------------------------------------------------------|--------------------|------|--------------------|------|

| Operating Voltage | VDD    |                                                                    | 3                  |      | 18                 | V    |

| Input Voltage     | VIH    | Annual SEC (1889) Law an along (1890) TE Parkinsking (1890) (1890) | 0.7V <sub>DD</sub> |      | V <sub>DD</sub>    | ٧    |

| Input Voltage     | VIL    |                                                                    | 0                  |      | 0.3V <sub>DD</sub> | ٧    |

| Analog Input Volt | VIA    |                                                                    | Vss                |      | VDD                | V    |

#### **Electrical Characteristics**

| H                                         |      |        | Conditions                                                                                          | Ta=- | -40°C | T,   | a=25              | °C   | Ta=  | + 85°C | 11-14 |

|-------------------------------------------|------|--------|-----------------------------------------------------------------------------------------------------|------|-------|------|-------------------|------|------|--------|-------|

| Item                                      |      | VDD(V) | Conditions                                                                                          | Min. | Max.  | Min. | Тур.              | Max. | Min. | Max.   | Unit  |

|                                           |      | 5      |                                                                                                     |      | 1000  |      | 225               | 1250 |      | 1440   |       |

| On-State Resistance                       | RON  | 10     | VIS=VDD-VSS                                                                                         |      | 145   |      | 85                | 180  |      | 200    | Ω     |

| On-State Resistance                       |      | 12     | VIS 2                                                                                               |      | 110   |      | 75                | 135  |      | 165    |       |

|                                           |      | 15     |                                                                                                     |      | 75    |      | 65                | 95   |      | 110    |       |

|                                           |      | 5      |                                                                                                     |      |       |      | 35                |      |      |        |       |

| On-State Resistance<br>Difference Between | ∆Ron | 10     | VDD-VSS                                                                                             |      |       | 1.5  | 20                |      |      |        | Ω     |

| Any Two Switches                          | ANON | 12     | $V_{IS} = \frac{V_{DD} - V_{SS}}{2}$                                                                |      |       |      | 18                |      |      |        | 12    |

|                                           |      | 15     |                                                                                                     |      |       |      | 15                |      |      |        |       |

| Input Leakage<br>Current                  | IL   | 18     | All<br>Switches OFF                                                                                 |      | ±100  |      | ±1                | ±100 |      | ±10000 | nA    |

|                                           |      | 5      | Switch ON                                                                                           | 3.5  |       | 3.5  |                   |      | 3.5  |        | V     |

| Input Voltage<br>(Logic)                  | VIII | 10     |                                                                                                     | 7    |       | 7    |                   |      | 7    |        |       |

| (Logio)                                   |      | 15     | RON <ron max.<="" td=""><td>11</td><td></td><td>11</td><td></td><td></td><td>11</td><td></td></ron> | 11   |       | 11   |                   |      | 11   |        |       |

|                                           |      | 5      | Switch OFF                                                                                          |      | 1.5   |      |                   | 1.5  |      | 1.5    |       |

| Input Voltage<br>(Logic)                  | VII  | 10     |                                                                                                     |      | 3     |      |                   | 3    |      | 3      | V     |

| (203.0)                                   |      | 15     | IL<0.2 μA                                                                                           |      | 4     |      |                   | 4    |      | 4      |       |

| Input Current                             | 11   | 18     | VI=VSS, VDD                                                                                         |      | ±0.1  |      | ±10 <sup>-3</sup> | ±1   |      | ±1     | μА    |

|                                           |      | 5      | 1.1                                                                                                 |      | 5     |      | 0.04              | 5    |      | 150    |       |

| Quiescent                                 | Inc  | 10     | VI-Voc Voc                                                                                          |      | 10    |      | 0.04              | 10   |      | 300    | μА    |

| Current                                   | IDD  | 15     | VI=VSS, VDD                                                                                         |      | 20    |      | 0.04              | 20   |      | 600    |       |

|                                           |      | 20     |                                                                                                     |      | 100   |      | 0.08              | 100  |      | 3000   |       |

## μPD22100C

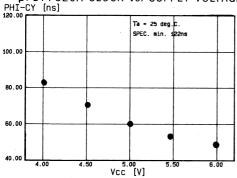

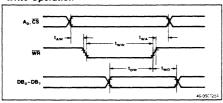

Switching Characteristics (Ta = 25 °C)

| Characteristics                                                           | Symbol  | VDD(V) |             | Conditions                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Min. | Тур. | Мах.                                                                                                                                                                                                                    | Unit         |

|---------------------------------------------------------------------------|---------|--------|-------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

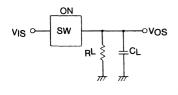

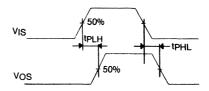

| Propagation<br>Set Up Time                                                |         | 5      | Signal IN   | NPUT → Signal (                                                       | OUTPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 30   | 60                                                                                                                                                                                                                      |              |

|                                                                           |         | 10     | RL=10       | $k\Omega$ , $C_L = 50 pF$                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 15   | 30                                                                                                                                                                                                                      | ns           |

|                                                                           | tPHL    | 15     | tr = tf = 2 | 20 NS                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 10   | 20                                                                                                                                                                                                                      |              |

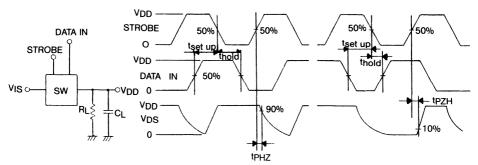

|                                                                           |         | 5      | Strobe II   | NPUT                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 300  | 600                                                                                                                                                                                                                     |              |

| Propagation  Set Up Time  Hold Time                                       | tPZH    | 10     |             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 125  | 250                                                                                                                                                                                                                     | ns           |

|                                                                           |         | 15     |             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 80   | 160                                                                                                                                                                                                                     |              |

|                                                                           |         | 5      | Data INF    | UT                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 110  | 220                                                                                                                                                                                                                     |              |

|                                                                           | tPZH    | 10     |             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 40   | 80                                                                                                                                                                                                                      | ns           |

| Set Up Time<br>Hold Time<br>Frequency                                     |         | 15     |             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 25   | 50                                                                                                                                                                                                                      |              |

|                                                                           |         | 5      | Address     | INPUT                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 350  | 700                                                                                                                                                                                                                     |              |

| Propagation                                                               | tPZH    | 10     |             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 135  | 270                                                                                                                                                                                                                     | ns           |

|                                                                           | VDD(V)  | 90     | 180         |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |      |                                                                                                                                                                                                                         |              |

| tPLi tPHI tPZi tPZi tPZi tPZi tPZi tPLi tPLi tPLi tPLi tPLi tPLi tPLi tPL |         | 5      | Strobe II   | NPUT                                                                  | $R_{\parallel} = 1 k\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | 165  | 330                                                                                                                                                                                                                     | ns           |

|                                                                           | tPHZ    | 10     |             |                                                                       | CL=50 pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | 85   | 170                                                                                                                                                                                                                     |              |

|                                                                           |         | 15     |             |                                                                       | RI = 1 kΩ CL = 50 pF Lr, tj = 20 ns  Ri = 1 kΩ CL = 50 pF Lr, tj = 20 ns  Ri = 1 kΩ CL = 50 pF Lr, tj = 20 ns  Ri = 1 kΩ Cl = 50 pF Lr, tj = 20 ns  Ri = 1 kΩ Cl = 50 pF Lr, tj = 20 ns  Ri = 1 kΩ Cl = 50 pF Lr, tj = 20 ns  Ri = 1 kΩ Cl = 50 pF Lr, tj = 20 ns  Ri = 1 kΩ Cl = 50 pF Lr, tj = 20 ns  Ri = 1 kΩ Cl = 50 pF Lr, tj = 20 ns  Ri = 1 kΩ Ri |      |      |                                                                                                                                                                                                                         |              |

|                                                                           |         | 5      | Data INF    | t IT                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 210  | 420                                                                                                                                                                                                                     |              |

|                                                                           | tPLZ    | 10     |             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 110  | 220                                                                                                                                                                                                                     | ns           |

|                                                                           |         | 15     |             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 100  | 200                                                                                                                                                                                                                     |              |

|                                                                           | -       | 5      | Address     | INPUT                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 435  | 870                                                                                                                                                                                                                     |              |

|                                                                           | tPHZ    | 10     |             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 210  | 420                                                                                                                                                                                                                     | ns           |

|                                                                           |         | 15     |             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 160  | 320                                                                                                                                                                                                                     |              |

|                                                                           |         | 5      | Data INF    | UT                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 95   | 190                                                                                                                                                                                                                     |              |

| Set Up Time                                                               | tset up | 10     | Strobe      | •                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 25   | 50                                                                                                                                                                                                                      | ns           |

|                                                                           |         | 15     | Addre       | IPUT → Signal OUTPUT   30   60   15   15   15   15   15   15   15   1 | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |      |                                                                                                                                                                                                                         |              |

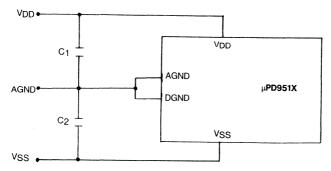

|                                                                           |         | 5      | Data INF    | UT                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 180  | 360                                                                                                                                                                                                                     |              |